Un equipo internacional, en el que también participan científicos de IBM Research en Zurich (Suiza), presenta en la revista Nature Electronics la celda de Memoria Dinámica de Acceso Aleatorio DRAM más pequeña jamás construida, 50 años después de su invención

Investigadores de la Universidad de Granada (UGR), junto con científicos de IBM Research en Zurich (Suiza), han presentado la celda de Memoria Dinámica de Acceso Aleatorio (DRAM) más pequeña jamás construida, cincuenta años después de su invención.

Las memorias DRAM se encuentran en todo tipo de aparatos electrónicos: desde grandes servidores de datos y ordenadores personales, hasta dispositivos portátiles, como tablets y smartphones y consolas de videojuegos.

En un nuevo artículo publicado en la prestigiosa revista NatureElectronics, los investigadores han presentado estas nuevas celdas DRAM, que presentan un consumo de energía potencialmente bajo y área pequeña sin precedentes. Por lo tanto, estas celdas son particularmente atractivas para la implementación en dispositivos móviles o como memoria caché en microprocesadores.

Las celdas de memoria DRAM consisten en un transistor MOSFET y un condensador. A su inventor, el científico de IBM Robert Dennard, se le ocurrió la idea de almacenar información en forma de carga eléctrica en un condensador controlado por un transistor a mediados de la década de 1960.

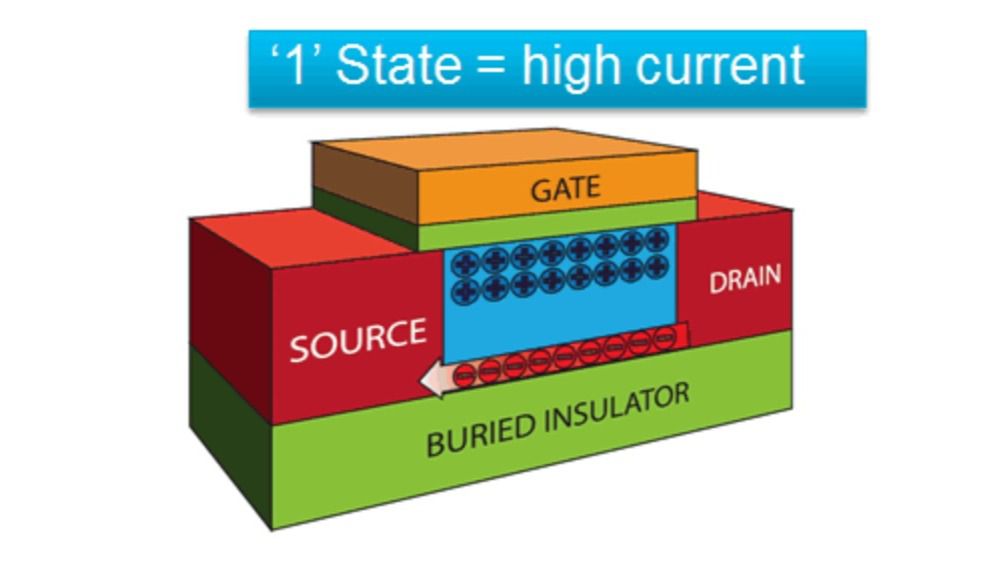

Los diferentes niveles de corriente asociados con la cantidad de carga almacenada en el condensador servirían para codificar los estados lógicos binarios 0 y 1. El condensador debe ser lo suficientemente grande como para almacenar una cantidad medible de carga. Por otro lado, la necesidad de una mayor densidad de almacenamiento por áreade silicio limita el crecimiento a lo largo de las dimensiones laterales. Esto ha dejado la tercera dimensión, la perpendicular a la superficie, como la única forma de aumentar el tamaño del condensador. Es por eso que la técnica habitual consiste en fabricar condensadores verticales en agujeros profundos y estrechos en el substrato de silicio.

Objetivo: retirar el condensador

Durante las últimas dos décadas, ha habido intentos de deshacerse del condensador, reduciendo así el área y el costo de fabricación de las células DRAM. Retirar el condensador se ha convertido casi en un imperativo para impulsar aún más la reducción del tamaño de la celda, lo que permitiría introducir mayor número de bits en el mismo área de silicio, esto es, más información almacenada a menor coste.

De seguir usando el condensador de almacenamiento, reducir el área de la celda sin disminuir la cantidad de carga que se puede almacenar deja solo una vía abierta para la fabricación: hacer condensadoresmuy profundos.

“A largo plazo, esto representa un cuello de botella, no solo debido a restricciones geométricas, sino también porque la acumulación de carga en la parte superior del «pozo» hace que sea más difícil utilizar toda la capacidad de almacenamiento”, señala el autor principal de esta investigación, el investigador del departamento de Electrónica y Tecnología de Computadores, Carlos Navarro Moral, contratado Juan de la Cierva-Incorporación.

En cambio, almacenar la carga en el cuerpo del transistor se ha identificado como la mejor estrategia para reducir aún más la escala. En los últimos años, se han estudiado experimentalmente diferentes variantes de células DRAM sin condensador utilizando silicio, pero se ha prestado muy poca atención a conceptos similares basados en materiales semiconductores alternativos.

En el artículo publicado en Nature Electronics, los investigadores de la UGR demuestran la celda de memoria DRAM sin condensador más pequeña jamás construida con una longitud de puerta física de sólo 14 nanómetros.

Este logro fue posible gracias a una colaboración entrela Universidad de Granada e IBM-ResearchLab en Zurich (Suiza), como parte del proyecto europeo de investigación «REMINDER» financiado por la Comisión Europea y coordinado por la UGR. Los transistores fabricados en IBM ResearchZurichLab utilizando el material III-V InGaAs fueron caracterizados eléctricamente por los investigadores de la Universidad de Granada, en el Laboratorio de Nanoelectrónica, Grafeno y Materiales Bidimensionales del CITIC-UGR, uno de los cuatro laboratorios singulares existentes en la UGR.

La celda fabricada es una celda DRAM de un solo transistor y sin condensador, que utiliza el cuerpo del transistor para almacenar temporalmente la carga eléctrica. La inyección y extracción de la carga eléctrica del cuerpo del transistor permite la modulación del comportamiento electrostático del transistor, lo que conduce a los dos niveles de corriente diferentes que representan a los niveles lógicos 0 y 1. Los materiales III-V, como InGaAs, ofrecen la ventaja potencial de operar a voltajes significativamente más bajos. Esto, a su vez, se traduce en un consumo de energía potencialmente mucho menor.